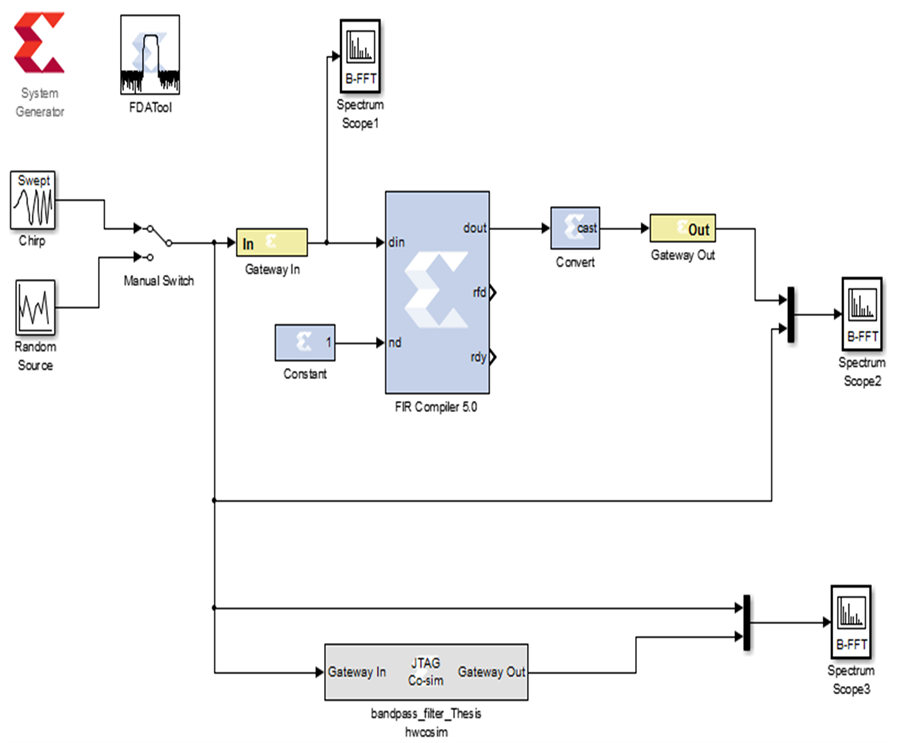

FPGA implementation of Reconfigurable FIR filters design with System... | Download Scientific Diagram

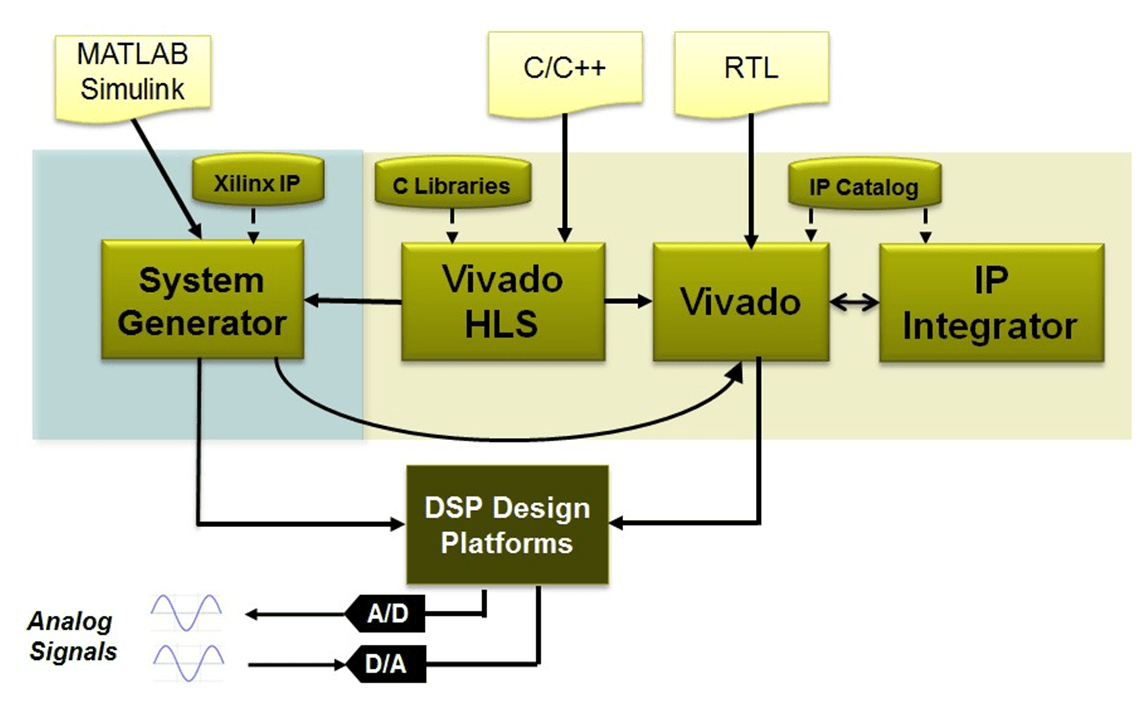

Design and Implementation of Efficient FIR Filter Structures using Xilinx System Generator | Semantic Scholar

PDF) FPGA Implementation of Higher Order FIR Filter | International Journal of Electrical and Computer Engineering (IJECE) - Academia.edu

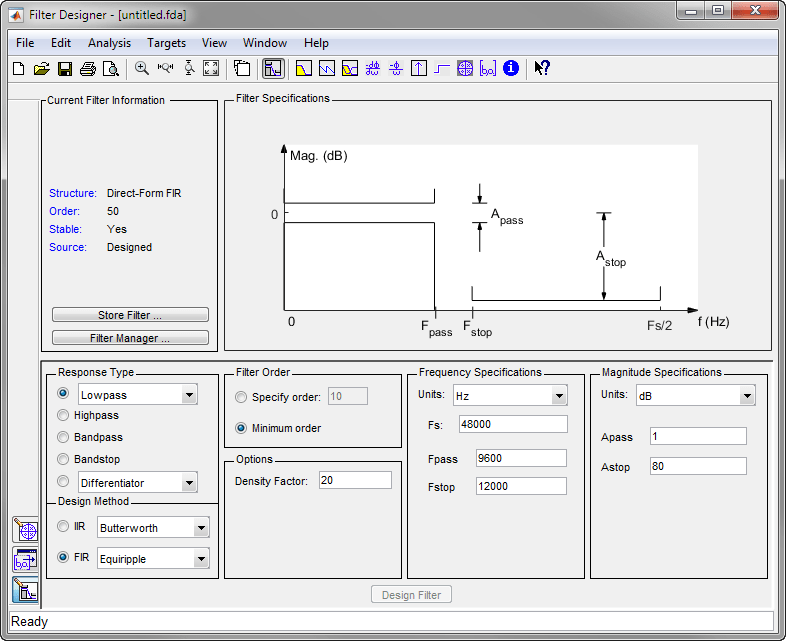

Design and Implementation of Low-Pass, High-Pass and Band-Pass Finite Impulse Response (FIR) Filters Using FPGA

Design and Implementation of Low-Pass, High-Pass and Band-Pass Finite Impulse Response (FIR) Filters Using FPGA

Design and Implementation of Low-Pass, High-Pass and Band-Pass Finite Impulse Response (FIR) Filters Using FPGA

Design and Implementation of Low-Pass, High-Pass and Band-Pass Finite Impulse Response (FIR) Filters Using FPGA

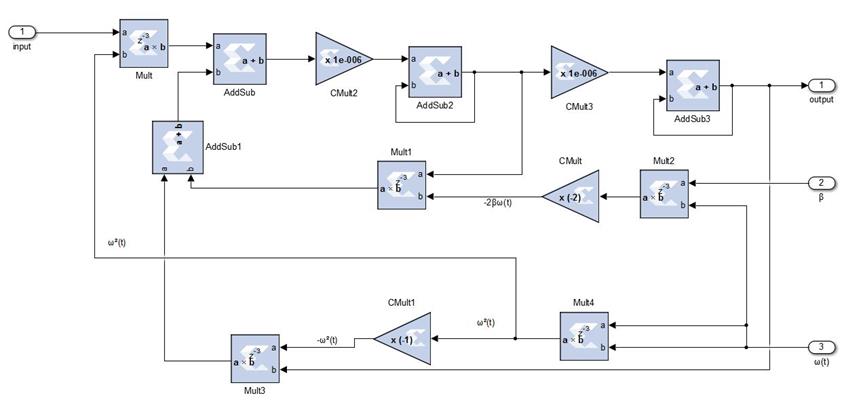

Figure 3 from Design and Implementation of Digital Butterworth IIR Filter Using Xilinx System Generator for Noise Reduction in ECG Signal | Semantic Scholar